# **USN**

# Third Semester B.E. Degree Examination, June/July 2014

## Logic Design

Time: 3 hrs. Max. Marks:100

Note: Answer FIVE full questions, selecting at least TWO questions from each part.

#### <u> PART – A</u>

- Construct a truth table and write the Boolean output equations in canonical POS and SOP 1 forms for the output P. P is to be true when the input variables x and y are true or when y is false but x and z are true. (06 Marks)

- Simplify  $T = w\overline{z} + xy\overline{z} + \overline{wxyz} + \overline{wxyz}$  using K-map in POS form. (06 Marks)

- Simplify  $R = f(a, b, c, d) = \sum m (2, 3, 4, 5, 9, 15) + dc (8, 10, 11, 13)$  using K-map and implement the circuit using NAND gates. (08 Marks)

- 2 Using Quine-Mc-Clusky's method, simplify the function,

$$f(A, B, C, D) = \sum_{n=0}^{\infty} f(0, 1, 5, 8, 9, 13, 14, 15).$$

(10 Marks)

Simplify using VEM technique the following expression,

$$V = f(a, b, c, d) = \sum m(0, 1, 4, 8, 9, 10) + dc(2, 11)$$

(10 Marks)

Realize the following functions using one 7418 decoder and extended gates: 3

$$P = f(x, y, z) = \sum_{z=0}^{\infty} (0, 4, 7)$$

$$Q = f(x, y, z) = \sum (3, 5, 6)$$

(08 Marks)

b. Realize 4:16 decoder using 3:8 (74138) decoders.

(06 Marks)

Write a note on priority encoder.

- (06 Marks)

- a. Implement the expression s = ad + bc + bd using 4:1 mux. Choosing b and d as select lines.

- b. Design a full adder using gates.

(10 Marks) (05 Marks)

Design a one bit comparator.

(05 Marks)

### PART - B

a. Explain the operation of Gated SR latch.

- (04 Marks)

- With the circuit diagram, explain the operation of pulse triggered Master Slave JK flip flop. b.

- With the circuit diagram, explain the working of positive edge triggered D flip flop.(10 Marks)

- 6 Derive the characteristic equation of T flip flop. a.

(02 Marks)

- Design a synchronous mod-6 counter using clocked JK flip flop with count sequence 0, 1, 2, b.  $3, 4, 5, 0, \dots$  in binary. (10 Marks)

- With the function table and circuit, explain the operation of universal shift register. (08 Marks)

7 a. Write the Moore state model notation of JK flip flop.

(06 Marks)

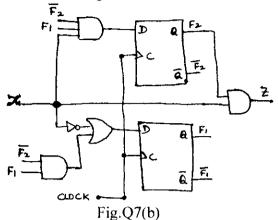

b. Write the characteristic equations, next state equation, output equation, transition table, excitation table, state table and state diagram for the circuit shown in Fig.Q7(b).

(14 Marks)

- 8 a. Construct the state diagram for a Mealy sequential circuit that will detect the serial input sequence x = 010110, when the complete sequence has been detected, then cause output z to go high. Assume the states as s<sub>0</sub>, s<sub>1</sub>, s<sub>2</sub>, ..... (10 Marks)

- b. Design a modulo-8 synchronous binary counter using D flip flops that will count the number of occurrences of an input; that is, the number of times it is a '1', the input variable x must be coincident with the clock to be counted. The counter is to count in binary. Assume the flip flop inputs as D<sub>3</sub>, D<sub>2</sub>, D<sub>1</sub> and outputs as F<sub>3</sub>, F<sub>2</sub>, F<sub>1</sub> respectively. (10 Marks)

\* \* \* \* \*